VOICE OF THE ENGINEER

Tales from the Cube: The case of the bad memory chip Pg 108

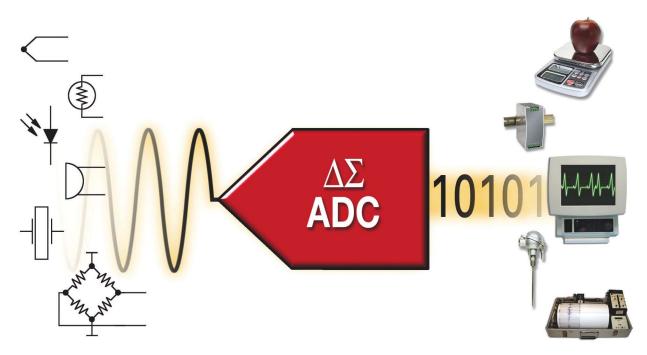

Bonnie Baker: Delta-sigma ADCs in a nutshell, part 4 Pg 30

> **Prying Eyes:** SanDisk V-Mate Pg 32

> > Design Ideas Pg 89

# THE 2008 DSP DIRECTORY PEEL AWAY THE LAYERS OF COMPLEXITY

MAR

Issue 6/2008

www.edn.com

page 44

#### PUSH FOR POWER EFFICIENCY FORCES CHANGES IN SERVER-CENTER HARDWARE AND SOFTWARE

Page 37

CLICK HERE TO **RENEW** your FREE <u>magazine</u> subscription CLICK HERE TO **START** a FREE <u>e-newsletter</u> subscription Using IC prototyping to optimize design implementation Page 63

TRIP POINTS FOR IC-TIMING ANALYSIS Page 77

DIGITAL TV FOR THE FUTURE: hybrid analog/ digital-TV-receiver design Page 83

# All the right tools in your hand.

#### **WaveJet® Oscilloscopes**

#### More tools. Better tools. The right tools.

The right tools make debugging faster and easier. The WaveJet 300 Series provides more tools and greater performance than other compact oscilloscopes in the 100 MHz to 500 MHz range.

C1MΩ

- Long Memory: 500 k/ch

- Large 7.5" Color Display

- Compact Size, only 4" Deep

- USB Connectivity

- Replay History Mode

- Frequency Counter

More than 300,000 products stocked and ready to ship today!"

Digi-Key Corporation purchases all product directly from its original manufacturer.

Quality Electronic Components, Superior Service

25% higher performance 29% lower power 1067-Mbps DDR3 support

# FULL THROTTLE

Stratix<sup>®</sup> III FPGAs, with blazing 1067-Mbps (533-MHz) DDR3 performance, are 25% faster than the competition while consuming 29% less power. With the highest density of any FPGA on the market, Stratix III devices allow you to integrate more functions in the same board space. Add Altera's Quartus<sup>®</sup> II software to the mix, and you'll complete designs in less time while meeting your power budgets. So, who wants to go faster?

Mbps

www.altera.com

#### **Enter the New World of Bourns**

Automotive Sensors Circuit Protection Solutions Magnetic Products Microelectronic Modules Panel Controls & Encoders Precision Potentiometers Resistive Products The world of Bourns has grown. An expanding world focused on exceeding our customers' needs. New innovative products and technologies. Expanded application solutions. Plus a worldwide team of technical experts to facilitate the design process and solve tough application problems. All provided to

help customers shorten design cycles and achieve faster time-to-market.

At Bourns, we have grown to serve you better. Step in – explore the new world of possibilities from Bourns today:

www.bourns.com/newworld

Bourns - the company you have relied on for more than 60 years.

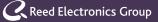

# Maximize Multicore

#### Increase Your Performance with NI LabVIEW

Application

Sequential C Program on Multicore

on Multicore

Using NI LabVIEW — an inherently parallel graphical programming language — you can take advantage of the latest advances in multicore systems, including real-time symmetric multiprocessing and FPGA-based embedded systems. LabVIEW simplifies visualizing and programming parallel applications for test, control, and embedded design. Using LabVIEW, customers are realizing up to a linear performance increase on their multicore systems.

#### >> Learn to maximize your multicore processor at ni.com/multicore

866 337 5041

# The 2008 EDN DSP Directory

This year's directory can help you to peel away the layers of complexity to find the perfect digital-signal processor for your project. by Robert Cravotta, Technical Editor

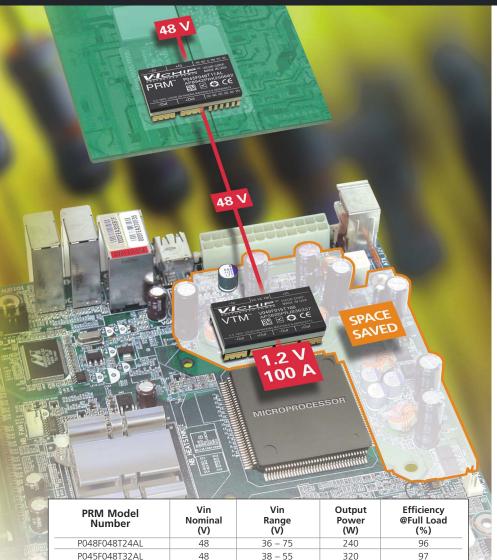

#### Push for power efficiency forces changes in servercenter hardware and software

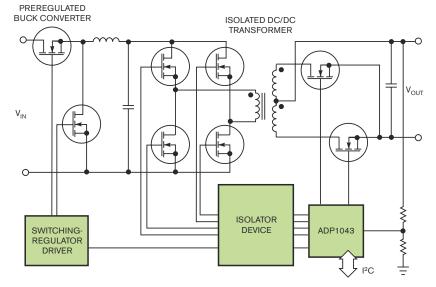

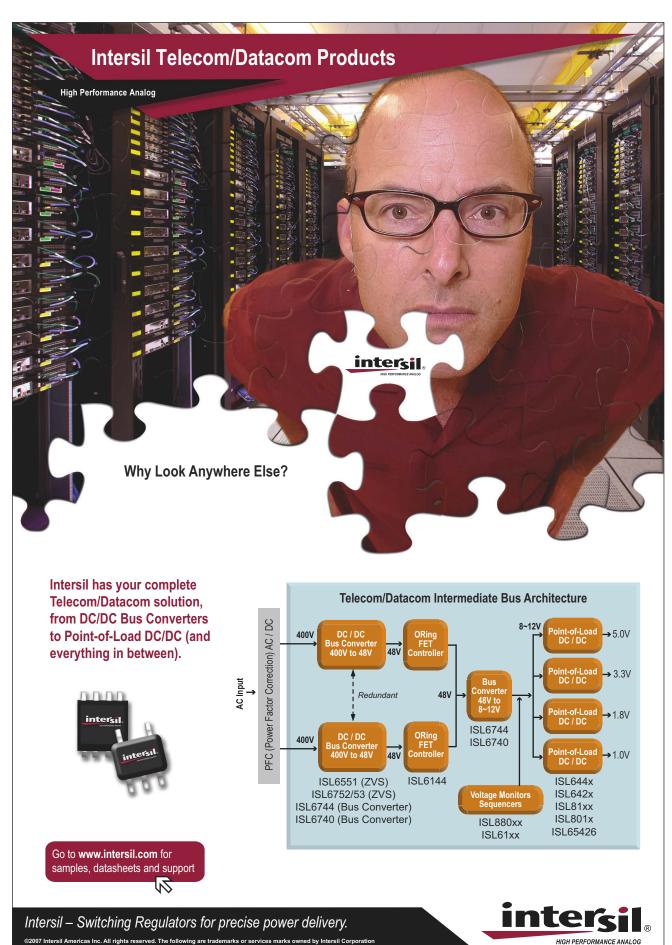

37 Industry initiatives have set the ambitious goal of halving datacenter energy usage by 2011. To achieve this objective, the industry must shift to the use of digitalpower control and management at the ac/dc- and dc/dc-powersupply level. by Margery Conner, Technical Editor EDN contents 3,20.08

#### Using IC prototyping to optimize design implementation

63 Making the right tradeoffs during IC prototyping can minimize risk and ultimately save time and money. by Neeraj Kaul and Steve Kister, Synopsys Inc

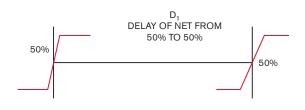

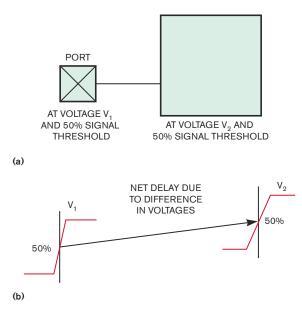

# Trip points for IC-timing analysis

Get the most out of your timing methodology. by Sunit Bansal, Ateet Mishra, and Naveen Sampath Krishna, Freescale Semiconductor

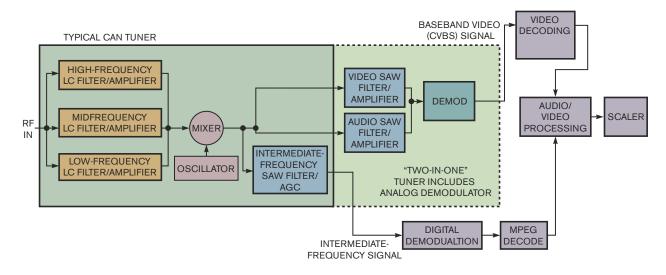

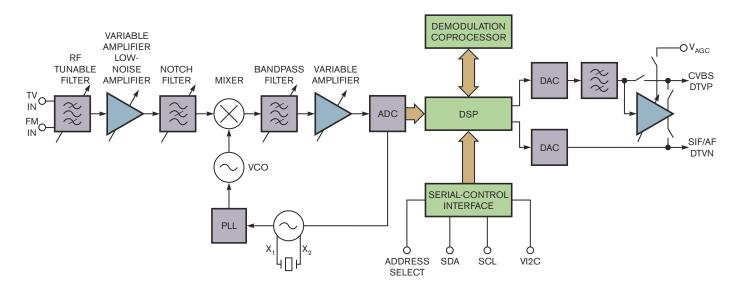

#### Digital TV for the future: hybrid analog/ digital-TV-receiver design

83 Analog TV hasn't disappeared yet, so you still need to understand it when designing hybrid analog/digital systems. by Brian D Mathews, Xceive Corp

# DESIGNIDEAS

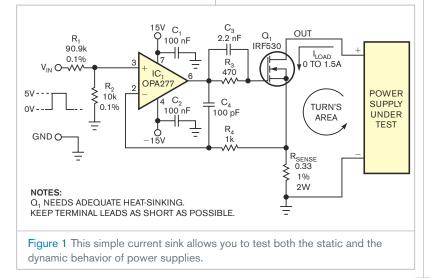

- 89 Precision voltage-controlled current sink tests power supplies

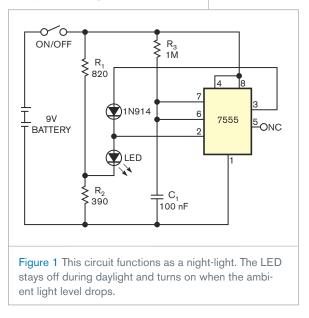

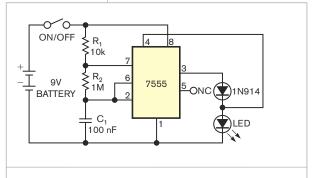

- 90 Red LEDs function as light sensors

- 92 White-noise generator has no flicker-noise component

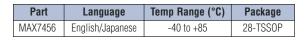

- 94 Analog voltage controls digital potentiometer

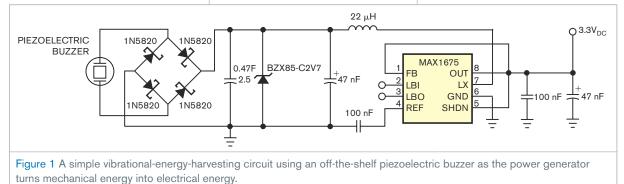

- 94 Harvest energy using a piezoelectric buzzer

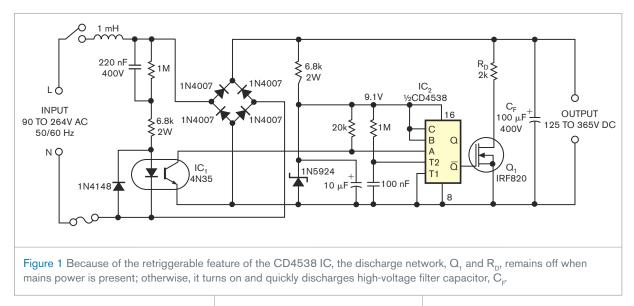

- 96 Retriggerable monostable multivibrator quickly discharges power-supply capacitor

#### Less is the new more.

contributes a large percentage of carbon emissions to our atmosphere. For many companies,

When you think of the major sources of global warming, do you think of portable electronics? Due to their popularity, the electronics industry now

the search for solutions is now critical. Actel is leading the way with its line of flash FPGAs which use far less power than conventional FPGAs. From the 5  $\mu$ W IGLOO<sup>TH</sup> family to the power management features of Fusion Programmable System Chips,

Actel's unique single-chip solutions save power at every level and in every mode. Find out how easy and affordable it is to dramatically reduce power consumption at actel.com. It's the least you can do.

## contents 3,20.08

- Customizable CPU platform combines DSP, FPGA

- 19 DSP with hardware acceleration transcodes HD in real time

- 20 Popularly priced scopes' display-update rates outpace competition

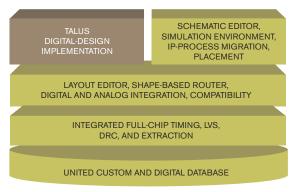

- 22 Magma takes on mixed-signal SOCs

- 24 Adaptive ICs optimize dc/dc-converter efficiency over wide load range

- 24 ADCs shrink in size, power for portable-scanner sockets

- 26 Spectrum analyzer brings real-time analysis to midrange applications

- **28 Voices:** Harley Feldberg: the pulse of the industry

#### DEPARTMENTS & COLUMNS

- 12 **EDN.comment:** External instruments here to stay

- 30 Baker's Best: Delta-sigma ADCs in a nutshell, part 4: noise versus data rate

- 32 Prying Eyes: SanDisk V-Mate video-memorycard recorder

- 108 Tales from the Cube: The case of the bad memory chip

#### PRODUCT ROUNDUP

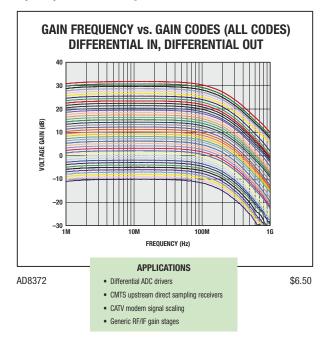

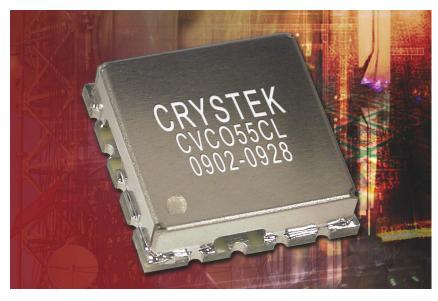

- 101 Amplifiers, Oscillators and Mixers: Voltagecontrolled oscillators, voltage-feedback amplifiers, audio-line drivers, and more

- 103 Computers and Peripherals: Graphics cards, optical-disc drives, mini-PCIe cards, solid-statedrive devices, and more

- 105 Test and Measurement: PCle cards

- 106 Embedded Systems: Low-power controllers, compactPCI PC series, general-purpose I/O cards, and more

EDN @ (ISSN#0012-7515), (GST#123397457) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer, Mark Finkelstein, President, Boston Division. Periodicals postage paid at Littleton, CO 80126 and additional mailing offices Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN ®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2008 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$165 one year; Canada, \$226 one year; (includes 7% GST, GST#123397457); Mexico, \$215 one year; air expedited, \$398 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario N9A 6N4. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN ®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN ® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 53, Number 6 (Printed in USA).

# The Newest Semiconductors

# online contents

HOME

NEWS CENTER

DESIGN CENTERS E

BUSINESS CENTERS

PART SEARCH MORE...

#### ONLINE ONLY

Check out these Web-exclusive articles:

#### Mobile operators seek a home for cost-effective 3G services

Mobile-telecommunications vendors are trying different tactics to encourage consumers to use their mobile phones at home, with the end goal of hooking customers on revenue-generating 3G data and multimedia services. The big question, however, is what these vendors can offer today to spur consumer enthusiasm and generate volumes high enough to bring costs down. One approach uses a femtocell, a small router that connects to a home's broadband connection. The other approach is to use Wi-Fi-enabled handsets for mobile calls at home and a specially designed Wi-Fi router connected to the Internet. →www.edn.com/article/CA6537588

#### Gartner halves 2008 semiconductormarket-growth estimate

→www.edn.com/article/CA6537489

#### Applied tips \$1.9M solar deal

→www.edn.com/article/CA6538013

#### Fiber-based energy harvester potentially turns garments into generators →www.edn.com/article/CA6535356

#### designideas READERS SOLVE DESIGN PROBLEMS

#### SUBMIT YOUR DESIGN IDEA

The Design Ideas section (pg 89 and www.edn.com/designideas) remains one of *EDN*'s most popular. But it doesn't write itself. So, if you've got a good idea, please submit it. You could get it published in *EDN*—and make \$150. →www.edn.com/info/30988.html

#### READER'S CHOICE

A selection of recent articles receiving high traffic on www.edn.com.

#### As SOCs grow, test-and-measurement instruments move on-chip

Complex ICs are not only absorbing more of the systems around them, but also swallowing the test equipment designers use to bring up, evaluate, and calibrate the chips.

→www.edn.com/article/CA6531583

#### Siemens cuts 3800 jobs, plans plant sales

Siemens AG lays out a restructuring plan that calls for some 3,800 job cuts as it moves its Siemens Enterprise Communications subsidiary from being a hardware supplier to a software provider in the harsh telecommunications market. →www.edn.com/article/CA6535492

#### Delta-sigma ADCs in a nutshell, part 3: the digital/decimator filter

A digital-filter function attenuates the noise, and the decimator function slows the output-data rate.

→www.edn.com/article/CA6531581

#### NE555 timer sparks low-cost voltage-to-frequency converter

The combination of an NE555 timer and a Miller integrator yields a voltageto-frequency converter that costs less than 50 cents.

→www.edn.com/article/CA6531584

#### Optoisolators compute watts and volt-amperes

Relying on the dynamic conductance of optoisolators' junctions, simple optoisolator bridges compute the watts and volt-amperes of an ac load. →www.edn.com/article/CA6531585

#### FROM EDN'S BLOGS

Thermal versus magnetic circuit breakers From Anablog, by Paul Rako

Because of an experience when I worked for GMC Truck and Coach 30 years ago, I have always thought that thermal circuit breakers were not very good. Yet, a recent experience with a thermal breaker seems to prove they work fine when you properly design and specify them. → www.edn.com/080320toc1

#### Staying on the Accelerating Technology Treadmill

From Brian's Brain, by Brian Dipert You might wonder why I'm holding onto any of my 802.11 adapters, given the commonality of integrated Wi-Fi nowadays. The short answer is that commonality doesn't yet equate to ubiquity. There are plenty of places in my home, for example, where running Category 5 cable would be a hassle and power-line networking might be sketchy.... → www.edn.com/080320toc2

#### DSP-directory gold mine Technical Editor Robert Cravotta's DSP directory is chock-full of hidden treasure. It includes **tables** that allow you to do side-by-side product comparisons and select just the right device for your project. It also includes information that expands greatly on the print edition. Do some mining of your own; you may find the mother lode. →www.edn/dspdirectory.com.

#### FAST-FORWARD YOUR MASTERPIECE.

Get your next big idea to market—faster. The built-in tools and technologies in Windows® Embedded help to accelerate development, so your teams get to put their efforts where they really count: creating the next generation of smart, connected devices. You also get Windows Embedded features that enable interoperability with industry standards and Microsoft® technologies, so you can build devices that easily connect to PCs, services, servers, and other devices. Learn more about how to fast-forward device development at: windowsembedded.com/fastforward

# Windows Embedded

#### BY RICK NELSON, EDITOR-IN-CHIEF

#### External instruments here to stay

recently commented on embedded instruments, noting that software that inserts testability structures into designs and that helps analyze test results to improve yield will become increasingly important as traditional instruments lose access to circuit nodes buried within deep-submicron ICs, multichip packages, and BGA-populated PCBs (printedcircuit boards). (See "Embedded instruments," *Test & Measurement World*, December 2007/January 2008, pg 7 www.tmworld.com/article/ CA6514353).

Then, EDN Executive Editor Ron Wilson addressed the topic from a chip-centric point of view (see "As SOCs grow, test-and-measurement instruments move on-chip," EDN, Feb 21, 2008, pg 31, www.edn.com/article/ CA6531583). In addition to citing lack of test-probe access, he notes that "As critical circuits reach gigahertz frequencies, it becomes physically impossible to get an accurate representation of signals off the die, even if you can probe the circuit." Nevertheless, he continues, manufacturing engineers must be able to develop lowcost test strategies, and designers must be able to create autocalibration routines that can compensate critical circuits for process, voltage, temperature, impedance, and noise variations while the chip is in use." He adds that "The only apparent option is to move the test-and-measurement instruments ... onto the chip itself."

Companies pursuing embedded-instrument strategies include DAFCA, Cisco, ARM, Analog Devices, Rambus, STMicroelectronics, Vitesse, and ASE. Wilson details the technologies of several of these companies in his article. The methods by which embedVerigy's purchase of Inovys speaks to the importance of the external hardware/software combination in testing today's state-of-the-art chips.

ded instruments communicate with the outside world, however, are just as important as the internal details of embedded-instrument technology.

Al Crouch, chief scientist at Inovys, now part of Verigy, addressed the migration of instruments into chips in an International Test Conference presentation last fall titled "The Need for Standard and Efficient Interconnection and Access of Embedded-Everything." In that talk, he noted that embedded instruments can serve in system-level test as well as chip-level test. A chip might work fine when you plug it into a \$10,000 load board that connects to a \$2 million ATE (automated-test-equipment) system, he said, but added that, when you pack it onto a  $5 \times 5$ -in. board with 10 other chips and connect it to a \$35 power supply, it might turn out not to work so well—an issue that embedded-system-level test can address effectively.

Crouch also commented that the proliferation of embedded instruments presents its own problems involving the need to effectively communicate with them. He concluded that the IEEE P1687 internal JTAG initiative can provide an effective way for orderly, standardized embedded-instrument communication and control.

Whatever the interface standard, real external instruments and systems that gather test data and external software that performs yield-learning and other analysis tasks must supplant embedded instruments. Verigy's purchase of Inovys speaks to the importance of the external hardware/software combination in testing today's state-ofthe-art chips.

Certainly, chip-test equipment is migrating from multimillion-dollar "big-iron" systems to something more cost-effective. The industry and media will address the pace of this evolution throughout the year. For instance, I'll be moderating a panel on this and other topics at the Third Annual GSC (Global Semiconductor Test Consortium) Conference, convening June 4 through 6 in San Diego, in partnership with the Design Automation Conference, convening the following week in Anaheim, CA. But whatever form the evolution takes, it would be a mistake to assume that embedded instruments will make external instruments go away.EDN

Contact me at rnelson@reedbusiness. com.

#### MORE AT EDN.COM

+ Go to www.edn.com/080320ed and click on Feedback Loop to post a comment on this column.

All values in stock If it's in our catalog, it's on our shelf

# 6 reasons to buy direct from Coilcraft

Because we're our own distributor, we guarantee that you can source any Coilcraft part with a single call.

We stock the latest RoHScompliant products and 99% of your orders ship the same day they're received!

Whether you need 10 pieces or 10,000, the one place to buy all your Coilcraft magnetics is Coilcraft Direct.

Talk directly to our engineers

Any part. Any quantity. Any time. 800-322-2645 buy.coilcraft.com

# Power That Gives You Best Of Both Technology Worlds

Switcher Efficiency Combined With LDO Noise And Transient Performance

The MIC38300 is a 3A step down converter and the first device in a new generation of SuperLNR<sup>™</sup> products providing the benefits of LDOs with respect to ease of use, fast transient performance, high PSRR and low noise while offering the efficiency of a switching regulator.

As output voltages move lower, the output noise and transient response of a switching regulator become an increasing challenge for designers. By combining a switcher whose output is slaved to the input of a high performance LDO, high efficiency is achieved with a clean low-noise output.

For more information, contact your local Micrel sales representative or visit us at: www.micrel.com/ad/mic38300. Literature: 1 (408) 435-2452 Information: 1 (408) 944-0800

#### The Good Stuff:

- ◆ 2.2A Continuous operating current

- ◆ Input voltage range: 3.0V to 5.5V

- Adjustable output voltage down to 1.0V

- Output noise less than 5mV

- Ultra fast transient performance

- Unique Switcher plus LDO architecture

- Fully integrated MOSFET switches

- Micro-power shutdown

- Easy upgrade from LDO as power dissipation becomes an issue

- Thermal shutdown and current limit protection

- ◆ 4mm × 6mm × 0.9mm MLF <sup>®</sup> package

@ 2008 Micrel, Inc. All rights reserved. Micrel is a registered trademark of Micrel, Inc. MLF is a registered trademark of Amkor Technology.

PRESIDENT, BOSTON DIVISION, REED BUSINESS INFORMATION Mark Finkelstein, mark.finkelstein@reedbusiness.com 1-781-734-8431

PUBLISHER, EDN WORLDWIDE Russell E Pratt, 1-781-734-8417;

rpratl@reedbusiness.com ASSOCIATE PUBLISHER, EDN WORLDWIDE Judy Hayes, 1-408-345-4437; judy.hayes@reedbusiness.com VICE PRESIDENT. EDITORIAL DIRECTOR

Karen Field, 1-781-734-8188; kfield@reedbusiness.com

EDITOR-IN-CHIEF, EDN WORLDWIDE Rick Nelson, 1-858-748-8418; rnelson@reedbusiness.com

EXECUTIVE EDITOR Ron Wilson, 1-408-345-4427; ronald.wilson@reedbusiness.com EDITOR-IN-CHIEF, EDN.COM

Matthew Miller 1-781-734-8446; fax: 1-303-265-3017; mdmiller@reedbusiness.com

> SENIOR ART DIRECTOR Mike O'Leary

1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@reedbusiness.com EMBEDDED SYSTEMS

Warren Webb, Technical Editor

1-858-513-3713; fax: 1-858-486-3646; wwebb@edn.com MASS STORAGE. MULTIMEDIA. PCs.

PRIPHERALS Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187;

bdipert@edn.com

MICROPROCESSORS, DSPs, TOOLS Robert Cravotta, Technical Editor

1-661-296-5096; fax: 1-303-265-3116; rcravotta@edn.com NEWS

Suzanne Deffree, Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

SEMICONDUCTOR MANUFACTURING AND DESIGN Ann Steffora Mutschler, Senior Editor

1-408-345-4436; ann.mutschler@reedbusiness.com

DESIGN IDEAS EDITOR Charles H Small edndesignideas@reedbusiness.com

SENIOR ASSOCIATE EDITOR Frances T Granville, 1-781-734-8439; fax: 1-303-265-3131;

f.granville@reedbusiness.com ASSOCIATE EDITOR

Maura Hadro Butler, 1-617-276-6523; mbutler@reedbusiness.com EDITORIAL/WEB PRODUCTION MANAGER

Diane Malone, Manager 1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney, Production/Editorial Coordinator 1-781-734-8442; fax: 1-303-265-3198 Melissa Annand, Newsletter/Editorial Coordinator *Contact for contributed technical articles* 1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-303-265-3042 34-8431 **CONTRIBUTING TECHNICAL EDITORS** Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

COLUMNISTS Howard Johnson, PhD; Bonnie Baker; Joshua Israelsohn; Pallab Chatterjee

PRODUCTION Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Jones, Production Manager 1-781-734-8328; fax: 1-303-265-3164

Linda Lepordo, Production Manager 1-781-734-8332; fax: 1-303-265-3015 EDN EUROPE

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

EDN ASIA Raymond Wong, Managing Director/ Publishing@ibi-asia.com Kirtimaya Varma, Editor in Chief kirti.varma@ibi-asia.com

EDN CHINA William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor johnmu@idg-rbi.com.cn EDN JAPAN

> Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community. DENNIS BROPHY

Director of Business Development, Mentor Graphics

DANIS CARTER Principal Engineer, Tyco Healthcare CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne DMITRII LOUKIANOV System Architect, Intel

> RON MANCINI Retired Staff Scientist GABRIEL PATULEA

Design Engineer, Cisco

Product-Line Director, Analog Devices SCOTT SMYERS

Vice President, Network and System Architecture Division, Sony TOM SZOLYGA

> Program Manager, Hewlett-Packard JIM WILLIAMS

Staff Scientist, Linear Technology

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.geffreemag. com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

# Sometimes, you have to outrun the competition.

VersaLogic's Cheetah Single Board Computer (SBC) delivers swiftness and agility to embedded computing applications. This

Pentium<sup>®</sup> M single board computer makes good on its promise of providing highperformance in a compact, ruggedized package. The Cheetah offers flexible RAM options and scalable processing for optimum application performance with minimal power

draw. Available in standard (0° to +60°C)

and extended (-40° to +85°C) temperature versions, the Cheetah features 10/100 Ethernet, high performance video capabilities, on-board CompactFlash® socket and extensive integrated I/O. Customization is available on quantities of 100 pieces or more.

Contact us and discover how for more than 30 years we've been perfecting the fine art of extra-ordinary support, and on-time delivery: One customer at a time.

#### PC/104 Product Offerings:

| SBC            | Lynx       | Puma      | Cheetah                |

|----------------|------------|-----------|------------------------|

| Processor      | Elan SC520 | AMD GX500 | Pentium <sup>®</sup> M |

| Max CPU Speeds | 133 MHz    | 500 MHz   | 1.6 GHz                |

| Cooling        | Heatsink   | Heatsink  | Fan                    |

| Extended Temp. | Y          | Y         | Y                      |

1.800.824.3163 1.541.485.8575 www.versalogic.com/che

# **COMPETITION ECLIPSED**

Imagine an industry first MCU capable of operating down to 0.9 V. Imagine solutions that are more power efficient than you thought possible. Imagine smaller form factors and lower system costs. Imagine best-in-class tools that enable immediate system design. Thanks to the remarkable engineering gains of our new line of MCU's, you can stop imagining and start creating your next great product.

#### WWW.SILABS.COM/POINT9

LOWEST VOLTAGE / GREATEST POWER EFFICIENCY HIGHEST FUNCTIONAL DENSITY / BEST-IN-CLASS TOOLS

INTRODUCING THE C8051F9xx: THE FIRST LINE OF MCUs DESIGNED TO OPERATE FROM A SINGLE-CELL BATTERY (0.9-3.6 V)

# ANALOG edge

#### **Designing with Electro-chemical Sensors**

#### **Application Note AN-1798**

#### Muna Acosta, Applications Engineer

As early as 1950, electro-chemical sensors were used for oxygen (gas) monitoring; however, with increasing concerns about personal safety, the demand for portable electro-chemical sensors has dramatically increased. Today, electro-chemical sensors are commonly used in portable equipment to detect different toxic gases.

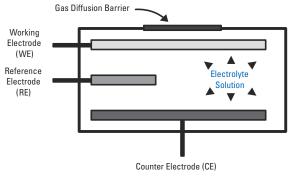

Electro-chemical sensors operate by reacting with monitored gas and producing an electrical current that is linearly proportional to the gas concentration. Older versions of electro-chemical sensors were based on a two-electrode configuration; however, to achieve superior electro-chemical stability, three-electrode systems are now used. The three electrodes are stacked parallel to each other, separated by a thin layer of electrolyte that provides ionic electrical contact between the electrodes.

#### **Sensor Functionality**

When a gas comes in contact with the sensor, it passes through a thin membrane barrier to reach the electrode surface. The first electrode that the gas comes in contact with is the Working Electrode (WE). The WE is designed to optimize the electro-chemical oxidation, (or reduction of the measured gas), and to generate a current flow that is proportional to the gas concentration.

The performance of the sensor deteriorates over time due to the continuous electro-chemical reaction of the changes in WE potential occurring on the electrode. To reduce deterioration while maintaining a constant sensitivity with a good linearity, a Reference Electrode (RE) is placed close to the WE. The reference electrode's purpose is to anchor the working electrode at the correct potential. In order for the RE to maintain a constant potential, no current should flow through it.

Figure 1. Typical Electro-chemical Sensor

The third electrode, the Counter Electrode (CE), conducts current into or out of the sensor cell. When the WE oxidizes carbon monoxide, the counter electrode reduces other molecules, such as oxygen to generate current. This current exactly balances the current generated at the WE. The ionic current between the working electrodes and counter is transported by the electrolyte.

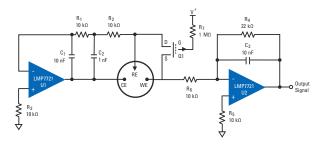

#### **Potentiostatic Circuit Operation**

Electro-chemical sensors require control circuitry to operate. The control circuitry is referred to as the Potentiostatic Circuit. *Figure 2* shows a simplified potentiostatic circuit which is comprised of two amplifiers and one JFET transistor. There are small variations in the implementation of this circuit, but the function and the outcome are the same.

#### Figure 2. Potentiostatic Circuit

The potentiostatic circuit's main purpose is to maintain a voltage between the reference electrode and the working electrode to control the electro-chemical reaction and to deliver an output signal proportional to the WE current.

When the sensor is exposed to the target gas, such as carbon monoxide, the reaction at the WE oxidizes the carbon monoxide to become carbon dioxide, which diffuses out of the sensor. Hydrogen ions and electrons are generated. The hydrogen ions migrate through the electrolyte towards the counter electrode. This process leaves a negative charge deposited on the working electrode. The electrons flow out from the working electrode through resistor R6 to the inverting input of the amplifier (U2). The amplifier

is configured as a transimpedance amplifier, which will convert the signal current from the WE into a voltage proportional to the applied gas concentration.

#### Output Voltage = I<sub>sensor</sub> (R4+ R6)/R4

For example, a 10 ppm carbon monoxide sample produces a typical signal current of approximately 500 nA, which will give an output voltage of 5 mV. The hydrogen ions that have migrated toward the counter electrode will lift the potential of the RE and the WE. This small rise in potential at the RE is measured by the control amplifier (U1). The amplifier will sink or source adequate current to the CE to balance the current required by the working electrode.

The P-type JFET is used as a switch to prevent the sensor from polarizing when the circuit has no power. If the sensor is polarized, it will take the sensor a long time to stabilize at equilibrium. The JFET is only active when the power is off and at this time it shorts the WE and RE to ensure that the working electrode is maintained at the same potential as the reference electrode.

#### **Amplifier Selection is Critical**

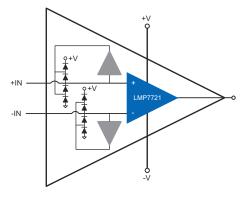

The performance of the potentiostatic circuit is greatly dependent on the electrical parameters of the amplifiers chosen. Designing a potentiostatic circuit using a high-bias current amplifier without precision specifications will impact the sensor sensitivity and increase sensor to sensor variation. A precision, ultralow input bias current amplifier, such as National's LMP7721, improves the potentiostatic circuit's performance, which allows the electro-chemical sensor to detect low-gas concentration with high accuracy.

The LMP7721 is designed with input bias guard driver circuitry to dramatically reduce the input bias current over the common mode voltage range to a typical of 3 fA at room temperature. Guaranteed specifications of 20 fA at room temperature and 900 fA at 85°C makes the LMP7721 the lowest temperature guaranteed bias current amplifier available.

In the potentiostatic circuit, the input bias current of the control amplifier (U1) is one of the critical specifications. The inverting input of U1 which is connected to RE, can-

Figure 1. Typical Electro-chemical Sensor

not draw any significant current from the reference electrode. The LMP7721 ultra-low input bias amplifier will assure that the reference electrode will maintain constant potential by having less then 3 fA of bias current.

In addition, gas sensors have large capacitance, so significant currents can flow for small potential shifts; therefore, the offset voltage and offset drift over temperature are critical. A precision amplifier such as the LMP7721 with a maximum input offset voltage of 180  $\mu$ V, and temperature drift of 4  $\mu$ V/°C will enable more accurate current measurements. An amplifier with larger offset adds to the bias voltage of the sensor's working electrode causing more error.

In conclusion, the majority of gas sensors are three-electrode electro-chemical cells that generate current that is linearly proportional to the gas concentration. The generated current is measured and converted to a voltage by the potentiostatic circuit. The potentiostatic circuit also provides the current to the counter electrode to balance the current required by the working electrode. The electrical specifications of the amplifiers used in the circuit should be precision with ultralow bias current, such as National's LMP7721 amplifier.

#### For more information, visit: national.com/analogedge

#### References:

Alphasense Limited. (Feb 2003). "AAN105-03: Designing a Potentiostatic Circuit." Feb 14, 2008. http://www.alphasense.com/pdf/AAN\_105.pdf

Chou, Jack. (1999). Chapter 2 "Electrochemical Sensors." Hazardous Gas Monitors: A Practical Guide to Selection, Operation and Application. (pp 27-35). McGraw-Hill and SciTech Publishing.

#### National Semiconductor 2900 Semiconductor Drive Santa Clara, CA 95051 1 800 272 9959

Mailing Address: PO Box 58090 Santa Clara, CA 95052

#### EDITED BY FRAN GRANVILLE

#### **INNOVATIONS & INNOVATORS**

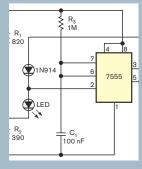

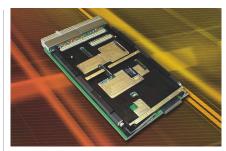

# Customizable CPU platform combines DSP, FPGA

ritical Link recently announced the MityDSP-Pro customizable processing platform, which targets data- and processing-intensive applications, including embedded radar control and signal processing, high-data-rate real-time data acquisition, image processing, and fine-tolerance manufacturing test. The standard module integrates a 1.2-GHz Texas Instruments (www.ti.com) TMS320C6455 DSP with a Xilinx (www.xilinx, com) XC3S2000 Spartan 3 FPGA, flashmemory and DDR2 SDRAM subsystems, and support for four one-lane serial-RapidIO links. Both the DSP and the FPGA can load and execute programs and logic images that end users develop.

"The MityDSP-platform approach enables a project to begin with 80% of the work complete by using an off-the-shelf CPU module and existing interface designs," says Tom Catalino, the company's vice president. These elements quickly provide the combination for a

The MityDSP-Pro reconfigurable-CPU platform collects, processes, and delivers data at processor speeds as high as 1.2 GHz.

custom application without the cost or scheduling problems of ground-up design, he says. The platform supports analog-to-digital, digitalto-analog, Ethernet, and general-purpose-I/O interfaces. The MityDSP-Pro standard-version module sells for \$1295 (100).

-by Warren Webb Critical Link, LLC, www.criticallink.com.

# FEEDBACK LOOP "Only an analog engineer could be so down to earth!"

--Reader Madhav Dhaneshwar, commenting on Technical Editor Paul Rako's article about overengineering. Read more and add your own comments in *EDN*'s Feedback Loop, at www.edn.com/ article/CA6518684.

#### DSP with hardware acceleration transcodes HD in real time

exas Instruments recently unveiled the TMS320DM6467 chip, the latest in the company's DaVinci DSP line. The chip targets use in real-time-video transcoding; it handles highdefinition video. The chip has an ARM core for control processing—in this case, a 926EJ-S—and a 600-MHz C64x+ DSP core. This variant includes a video coprocessor into which TI hard-coded transcoding-HD video, a conversion engine, and appropriate videointerface ports.

It performs simultaneous multiformat HD encoding, decoding, and transcoding of 1080p at 30 frames/sec or 1080i/720 at 60 frames/sec. The coprocessor and hardware acceleration deliver power equivalent to 3 GHz in a programmable DSP; offloading the main DSP engine in this way leaves more than half of its processing capability available for application code. The conversion engine also hosts hardware chroma sampling and handles overlay of menus. Target markets are media gateways, video telephony, and video security, in which the system handles multiple channels of standard-definition video. In this scenario, the set-top box becomes tomorrow's "digital-media adapter," routing video to and from any format, from big-screen HD to cell-phone displays.

The processing load that this chip handles would previously have required three 6415T DSPs, with more associated RAM and fl ash memory and a larger FPGA. The new part sells for \$35.95 (50,000). TI supports it with its standard tool chain, accessing third-party software intellectual property; an evaluation module runs MontaVista Linux. —by Graham Prophet

>Texas Instruments, www.ti.com.

# pulse

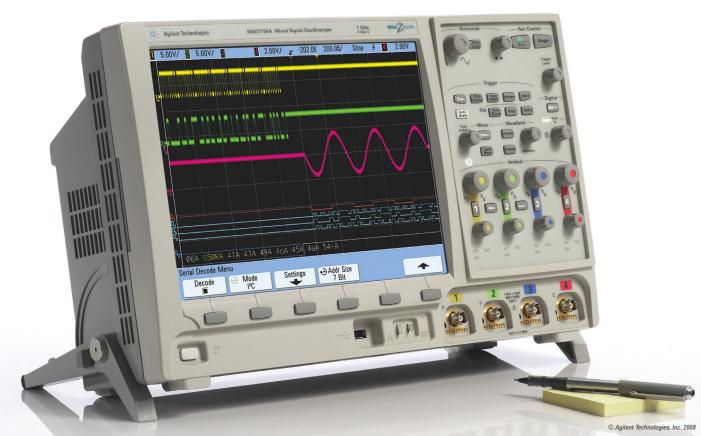

# Popularly priced scopes' display-update rates outpace competition

gilent Technologies has expanded its MSO (mixed-signal-oscilloscope)- and DSO (digital-storage oscilloscope)-product lines with 10 models in the nextgeneration InfiniiVision 7000 Series. The units deliver what the company calls an unparalleled deep-memory displayupdate rate of 100,000 waveforms/sec. The new series offers bandwidths as high as 1 GHz, analog-signal-sampling rates as high as 4G samples/ sec on each active channel, and memory depths as great as 8M points/channel with half of the analog channels and none of the MSOs' digital channels active. All models are in 7-in.deep packages that weigh 14 lbs and feature the industry's largest displays—12.1-in. XGA (1024×768-pixel) LCDs whose area is more than 35% greater than those of competitive scopes.

To appreciate how much faster the 7000 Series units update their displays than do competitive instruments, you need to perform a sideby side comparison, and you may initially wonder why Agilent makes such a big deal of display-update rate. But if you wait a few minutes and closely observe the displays, you should be impressed. In a

With a display whose resolution is greater than that of competitive instruments and whose area is more than 35% larger, the popularly priced InfiniiVision 7000 Series MSOs and DSOs provide a better view of your data. But the units' tour de force is their dramatically higher screen-update rates, which can bring elusive low-duty-rate phenomena to light in a tiny fraction of the time the competitive units require. demo at EDN's offices, a glitch appeared on the 7000 Series MSO display after about 3 seconds, whereas it took a competitive MSO more than five minutes to display an identical glitch in the same signal. In fact, the glitches occurred periodically at a low duty cycle, but, if you wait a predetermined interval for the glitch to appear on screen, the smaller the fraction of the time the scope is "blind," the higher its probability of displaying such a glitch. "Blind time" refers to periods when a scope processes data it has already acquired and can't acquire new data. In the 7000 Series, Agilent has dramatically reduced blind time and has thus correspondingly increased the percentage of time during which the scope can acquire new data.

The math says that we might occasionally have had to wait for more than two hours for the competitive scope to display the glitch. Joel Woodward, the Agilent senior product manager who conducted the demo, says that measurements he made at his office confirmed his two-hour prediction. His point, though, was that if we hadn't known that the glitch existed, it was highly unlikely that we would we have waited long enough to notice it. Yet, finding

infrequently occurring glitches that you don't know exist is a key function of scopes used for troubleshooting. Because they spend so much more of their time on signal acquisition, the 7000 Series scopes dramatically reduce the time required to find glitches, metastable states, and other elusive phenomena. And, because few engineers will wait for hours while nothing seems to be happening, the 7000s can reveal problems that competitive units simply miss.

Agilent also boasts that the 7000 Series offers the industry's most comprehensive suite of applications, including serial decoding and triggering for I2C (inter-IC), SPI (serial-peripheral-interface), CAN (controller-area-network), LIN (local-interconnect-network), and FlexRay buses; RS-232 and other UARTs; and rapid core-assisted debugging of designs that use Xilinx (www. xilinx.com) and Altera (www. altera.com) FPGAs. Other application-oriented features include segmented memory for analysis of laser pulses, radar bursts, and serial packets; offline PC viewing and sharing of previously acquired scope data; and RF-contextual viewing of scope data using vector-signal-analysis software.

US prices for InfiniiVision DSOs and MSOs range from \$6950 for a 350-MHz-bandwidth unit with two analog channels to \$17,900 for a 1-GHz-bandwidth MSO with four analog channels and 16 logic channels. A 500-MHz DSO with four analog channels costs \$11,050. All analog-only units contain the MSO hardware. To activate the MSO capabilities, you simply purchase a license.-by Dan Strassberg >Agilent Technologies, www.agilent.com/find/7000.

# **Delta-Sigma ADCs**

#### High Performance, Broad Portfolio – Enable Your Design

#### High-Performance Analog>>Your Way™

Low noise. Wide bandwidth. High speed. When your design needs best-in-class delta-sigma ADC performance, look to TI for high-performance devices to meet your design challenges.

| Device  | Description                                                                                                                              |

|---------|------------------------------------------------------------------------------------------------------------------------------------------|

| ADS1110 | Tiny, low power, 16-bit $\Delta\Sigma$ ADC with onboard reference and PGA (G=1, 2, 4, 8) in SOT: 2.048V ±0.05% accuracy, 5ppm/°C drift   |

| ADS1226 | Low-cost, easy-to-use 24-bit $\Delta\Sigma$ ADC: dedicated START pin, 100SPS data rate, $4\mu V_{RMS}$ low noise                         |

| ADS1232 | Ideal for weigh scales: 24-bit $\Delta\Sigma$ ADC, up to 23.5 effective bits, onboard PGA (G = 1, 2, 64, 128), 10SPS or 80SPS data rates |

| ADS1256 | Best-in-class 23-bit, noise-free $\Delta\Sigma$ ADC: 8 channels, 30kSPS and programmable digital filter (averaging)                      |

| ADS1258 | Fastest channel cycling, 24-bit, 125kSPS $\Delta\Sigma$ ADC: Measure all 16 channels in <675 $\mu$ s                                     |

| ADS1278 | Widest bandwidth, simultaneous sampling: 24-bit, 8-channel $\Delta\Sigma$ ADC, 128kSPS, 106dB SNR, ±0.0003% INL                          |

| ADS1281 | Ultra-low distortion 24-bit $\Delta\Sigma$ ADC: 130dB SNR and –122dB THD while consuming only 12mW of power, ±0.00006% INL               |

| ADS1610 | Fastest 16-bit $\Delta\Sigma$ ADC: 10MSPS, 86dB SNR, 5MHz wide and flat bandwidth                                                        |

| DDC232  | Highly integrated, current-input 20-bit $\Delta\Sigma$ ADC for measuring photodiodes, X-ray security and CT scanners: 32 channels        |

www.ti.com/deltasigma 1.800.477.8924 ext. 1434 — Get Datasheets, Samples and Evaluation Modules

# pulse

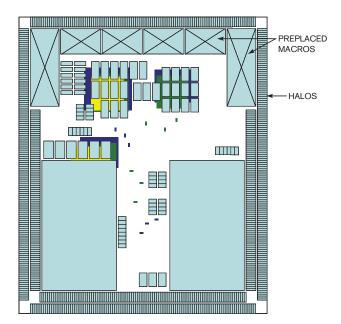

#### Magma takes on mixed-signal SOCs

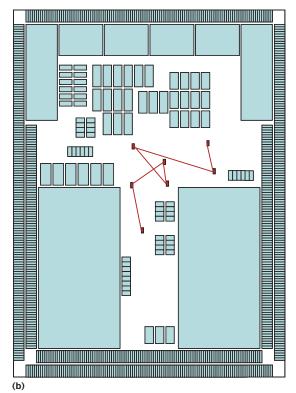

argeting consumer applications, SOCs (systems on chips) have in recent years integrated more and more analog circuitry. The circuits in question have been not merely the unavoidable PLLs and high-speed I/Os, but also control loops and precision signal paths spanning both audio and video. This situation has forced SOC designers into the world of mixed-signal design. To date, there have been two main approaches: One is to outsource the analog-block designs, import them again as hard IP (intellectual property), and hope that they work. The other approach is to use tool suites, such as Cadence's (www.cadence.com) Virtuoso, targeting skilled analog designers but integrating digital flows. This approach allows analog experts on the SOC team to do a custom analog design in the same database the digital folks are using for the rest of the SOC design, somewhat easing integration and verification.

Magma Design Automation recently introduced another alternative-one in keeping with the company's guiding concept that modest designs shouldn't require immodest expertise or license fees. The Titan platform will provide an environment in which not-full-custom analog design can proceed in parallel with digital design, merging during the physical design back end and working from a unified database. According to Ashutosh Mauskar, Magma's vice president of product and business development, Titan provides two paths by which a team can create analog designs. One is a schematic editor, from which the circuit description binds to foundry-de-

The Titan platform integrates an approach to analog design with the Talus design flow.

vice models to create a simulatable netlist. The other is an IP-oriented scheme, in which Magma defines commonly used analog functions in a topology template and a set of constraint equations. "The circuits will come right out of a textbook on analog design," Mauskar says, "so they will be familiar and useful."

The template-and-equation format allows Titan's process-migration tool to explore a range of alternative implementations in a new process technology within the constraints, offering designers their choice of migrated circuit designs. Thus, migrating an analog function in the Magma library to a new process node-although not exactly pushbutton-will be heavily automated. Working with the schematic and template tools, Titan will offer an analog-simulation environment that Magma based on the FineSim analogplacement tool. At this point, the isolation of the analog and digital designs ends, and both the simulated and placed analog netlist and the digital Talus netlist flow into a merged tool suite. That suite begins with a layout editor and a shapebased router that understands analog-circuit constraints, such as shielding styles and linelength control, preserving the operating characteristics of at least conservatively drawn analog circuits through the routing process.

The final stage in the flow is an extraction, timing, and checking stage. For this stage, Magma has incorporated its full-chip digital-timing tools: LVS (layout-versus-schematic) checking, DRC (design-rulechecking), and extraction. Although these concepts are familiar for digital designs, performing a full-chip LVS or extraction for an SOC with analog blocks is a different matter. LVS checking for analog circuits, for instance, requires rules decks from both the user and their foundry, according to Mauskar. Extracting analog components and model parameters from shapes is an unsolved problem, so the tools need this additional data. And extraction, which can use simple approximations for digitaltiming purposes, also becomes far more complex in the analog domain. Magma employs a new transistor-level extraction tool based on the company's QuickCap capacitance extractor. Again, analog extraction is a work in progress, and future developments should use the

detailed extraction algorithms that cell designers use.

All of the data for both the analog and digital nets goes into a unified database that complies with Open Access, reducing the version-control problems that can plague mixed-signal SOCs when the analog and digital designs proceed in isolation. The Titan approach addresses a number of the problems with mixed-signal SOC flows, but it is not a panacea, a universal custom design tool, or a substitute for having skilled analog designers, Mauskar warns. The template-based approach to analog-circuit design is more than adequate for normal, moderate-performance circuits, but it does not push a process node to its physical limits or implement science projects. It is for moderate-performance functional blocks. The migration tool also does not intervene in a circuit topology to find a better approach for a sigma-delta converter at 65 nm, for example. "The tools should work well with any technology node you can characterize accurately," Mauskar says. "But there is no way to replace human intelligence on the most demanding requirements. That's not what we are trying to do."

Magma is phasing the rollout of Titan over the course of the year. This quarter will see release of the Titan schematic capture, mixed-signal-layout and -routing, and chip-finishing tools. Magma will release the rest of the flow, including the analog-circuit templates and migration tool and the mixedsignal floorplanning tool, in beta form this quarter, and in production versions in the third quarter of this year.

-by Ron Wilson

Magma Design Automation, www.magma-da.com.

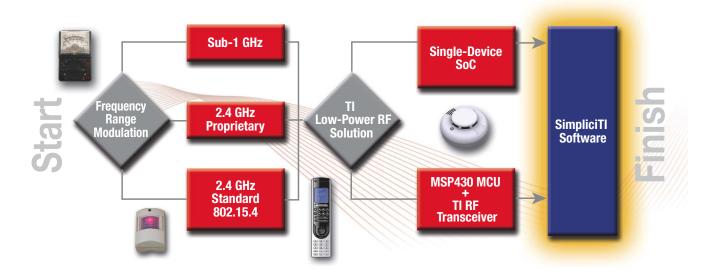

# SimpliciTI<sup>™</sup> – RF Made Easy

#### Network Protocol for Sub-1 GHz, 2.4 GHz and IEEE/802.15.4 RF ICs

High-Performance Analog>>Your Way™

**SimpliciTI** is a low-power RF protocol aimed at simple, small RF networks. This open-source software is an excellent start for building a network with battery-operated devices using one of TI's low-power RF SoCs or the MSP430 ultra-low-power MCU and a TI RF transceiver. SimpliciTI network protocol supports alarm and security systems, automatic meter reading, smoke detectors, home automation and active RFID applications.

#### SimpliciTI works with the following low-power RF devices and tools:

| Product      | Description                                                                                                                                                                                                                                          |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CC1101       | Sub-1 GHz, highly integrated, multi-channel RF transceiver designed for low-power wireless applications                                                                                                                                              |  |

| CC111x       | Sub-1 GHz System-on-Chip with enhanced 8051 MCU, up to 32 kB programmable Flash memory and optional USB                                                                                                                                              |  |

| CC2520       | Second-generation 2.4 GHz RF transceiver for proprietary and ZigBee <sup>®</sup> /IEEE 802.15.4 RF ICs with state-of-the-art selectivity/co-existence, excellent link budget, extended temperature range (-40°C to +125°C) and low-voltage operation |  |

| CC2430       | 2.4 GHz System-on-Chip specifically tailored for IEEE 802.15.4 and ZigBee applications. CC2430 comes in three different flash versions, 8F, 16F and 32F, with 32/64/128 kB of Flash memory, respectively                                             |  |

| CC2500       | 2.4 GHz RF transceiver designed for low-power wireless applications in the 2.4 GHz ISM band                                                                                                                                                          |  |

| CC251x       | 2.4 GHz, low-power System-on-Chip with integrated MCU, up to 32 kB Flash memory and optional full-speed integrated USB                                                                                                                               |  |

| eZ430-RF2500 | USB stick-based development tool combining the ability of the ultra-low-power MSP430 with low-power RF transceiver in a single device                                                                                                                |  |

Development kits are available for all products.

www.ti.com/simpliciti 1.800.477.8924 ext. 4354 Download Software Today!

# pulse

# Adaptive ICs optimize dc/dc-converter efficiency over wide load range

t can be a straightforward task to design a power supply for high efficiency at a single load point. Designing for high efficiency over a wide load range is a significant challenge, however. Organizations such as Energy Star (www. energystar.gov) specify minimum-efficiency levels of 100, 50, and 20% of full load for the ever-increasing minimum efficiencies that telecom and data-center computers require. Addressing this need, Zilker Labs' new ZL2004/2006 digital-dc-power controllers

The ZL2006/2004 uses proprietary control algorithms to optimize dc/dc-converter efficiency over widely varying loads. use proprietary algorithms to optimize converter efficiency over changing loads. Like the earlier versions of the converter family, the ZL2004/2006 features a digitally closed PWM (pulse-width-modulated) control loop.

These control-loop algorithms result in a full-load efficiency improvement as great as 3% and a light-load efficiency increase greater than 15% in typical applications, thus reducing peak power dissipation by as much as 20%. The chips automatically adapt their performance characteristics to increase the operating efficiency of the system when the load drops without sacrificing peak efficiency at heavy loads at which thermal concerns become important. The ZL2006 integrates 3A MOS-FET drivers that can support loads in excess of 40A; The ZL2004 requires external-drive MOSFETs.

In addition to the adaptive-

For higher currents, you can parallel multiple devices in a multiphase configuration.

load algorithms, the ZL2004/ 2006 includes adaptive-diode emulation: As the load current falls, traditional synchronous step-down converters begin to sink current to maintain regulation, drawing current from the output capacitor and reducing efficiency. The ZL2006 and ZL2004 detect this point and prevent the lower MOSFET from turning on and pulling current from the capacitor, resulting in a 5 to 10% efficiency improvement at load currents of less than 1A. Another of the chips' means of increasing efficiency at light load levels is to reduce the operating

frequency within a predefined range based on load-current changes.

For higher currents, you can parallel multiple devices in a multiphase configuration to achieve higher total load current than a single chip can support. As load demand decreases, the ZL2004/2006 can automatically optimize efficiency over the entire load range by turning off one or more phases in response to the load. Multiple devices can communicate through the single-pin digital-dc bus for nonhosted control of current-sharing and phase-sequencing. For a hosted power-management configuration, the chips support PMBus commands.

The ZL2006 has a 3 to 14V input range and a 0.54 to 5.5V output range and comes in a 6×6-mm, 36-lead QFN package. The ZL2004 has a 3 to 16V input range and a 0.54 to 4V output range and comes in a 5×5-mm, 32-lead QFN package. Prices start at \$2.95 (1000).-by Margery Conner ▷Zilker Labs, www. zilkerlabs.com.

#### ADCs SHRINK IN SIZE, POWER FOR PORTABLE-SCANNER SOCKETS

Texas Instruments' analog-products group has introduced the ADS5281, ADS5282, and ADS5287 series of ADCs featuring 10- and 12-bit resolution and sampling speeds as high as 65M samples/sec. The units come in octal format-that is, eight per package-for compactness and low power consumption. The devices target use in medical imaging, such as ultrasound and MRI (magnetic-resonance imaging), wireless communications, military guidance, automatic-test equipment, and video.

At 65M samples/sec, the ADS5281 family uses 77 mW/channel. With dynamic scaling, at 30M samples/ sec, the per-channel power drops to 48 mW. The chips interface directly with TI's recently introduced VCA8500 octal-variable-gain amplifier, which exhibits 0.8-nV/  $\sqrt{\text{Hz}}$  input noise for a 63-mW-per-channel power consumption. The ADC-and-octal- amplifier pairing constitutes a complete medical-signal-chain device with better noise performance and lower power than alternative

offerings, TI claims. Both parts come in 64-pin,  $9 \times 9$ -mm QFN packages for high-density systems.

The family of parts features a low-frequency noisesuppression mode that eliminates flicker noise, improving SNR (signal-to-noise ratio) by as much as 4.2 dB over a 1-MHz band in baseband and time-domain applications. Overload-recovery circuitry allows each ADC to provide valid data within one clock cycle after an input overload as high as 6 dB, allowing for immediate signal recovery and processing. You can program the devices' gain from 0 to 12 dB, driving full-scale outputs for input signals as low as 0.5V p-p.

TI also supplies the ADCs in an 80-pin TQFP that provides an easy transition to these next-generation devices, because it is pin-for-pin compatible with the previous-generation ADS527x family. Prices range from \$40 to \$68.60 (100), depending on speed and resolution. The octal amplifier costs \$40.-by Graham Prophet Texas Instruments, www.ti.com.

# <text>

Agilent 33220A/33250A Function and Arbitrary Waveform Generator

**FREE** Arbitrary Waveform Library www.agilent.com/find/any\_wave If you see a function generator in use today, the odds are it's an Agilent. Why is Agilent the best-seller?

Versatility. Our generators produce the most powerful array of waveforms in the industry. They include all the functions you'd expect, with pulse and arbitrary waves of up to 64k points—accurate, stable, low noise. And the 33220A is the first arb function generator designated LXI compliant.

Right now, you can get our Arbitrary Waveform Library absolutely free. The library includes 20+ waveforms that can be used immediately or modified to suit your own applications.

It's your deal. Call today to learn more, or visit us at <a href="http://www.agilent.com/find/any\_wave">www.agilent.com/find/any\_wave</a>

Agilent Authorized Distributor

1-800-FUTURE-1 www.futureelectronics.com//promos/agilent/t&m/

# pulse

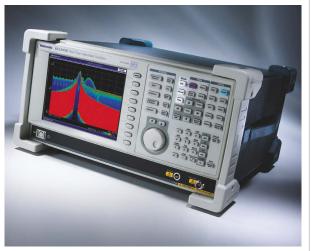

# Spectrum analyzer brings real-time analysis to midrange applications

ektronix has announced the RSA3000B family of real-time spectrum analyzers, which bring the company's DPX waveform-image-processing technology to midrange spectrum analysis. The RSA3300B series and RSA3408B provide a live-RF view of the spectrum, enabling an unprecedented RF-signal-discovery capability for a broad range of digital-RF applications, including RFID (radio-frequency identification), mobile communications, and spectrum management. DPX rapidly transforms volumes of data to produce live-RF-spectrum displays that reveal previously unseen RF signals and signal anomalies.

The rapid expansion of digital-RF applications has driven the measurement needs of many applications beyond the capabilities of traditional swept-spectrum and vectorsignal analysis. Digital-RF signals carry complex modulation that can change from one instant to the next, hopping frequencies, spiking briefly, and then disappearing. These transient and time-varying transmission techniques help RF devices to avoid interference, maximize peak power, and-often-evade detection.

According to Rick King, Tektronix's vice president of real-time-spectrum-analysis products, these analyzers are the first to solve problems that digital-RF technologies create. "Combining the highperformance RSA6100A series' DPX technology and live RF with a broad range of application-specific measurements makes the midrange RSA3300B series and RS-

The RSA3000B family leverages the manufacturer's DPX realtime-signal-processing technology–which, in spectrum analyzers had been available only in more expensive products–to present stunning displays that make short work of finding elusive anomalies in digital-RF spectra to 8 GHz.

A3408B the best choices not only for the toughest RF-discovery and -debugging problems, but also [for use as] as everyday spectrum-analysis and system-characterization tools," he says.

With a spectrum-processing rate hundreds of times as great as those of other vendors' spectrum analyzers, the new RSA3408B and RSA-3300B-series units provide 100% probability of intercept for transients as brief as 31 and 41 µsec, respectively. The units combine the exclusive ability to trigger on transient signals in both the time and the frequency domains with unmatched troubleshooting and debugging of digital-RF designs.

The RSA3300B series is available with frequency coverage of either dc to 3 GHz or dc to 8 GHz. With 15-MHz capture bandwidth and 70-dB SFDR (spurious-free dynamic range), the RSA3300B units suit designing and debugging of 3G mobile systems; nearfield systems, such as RFID and Bluetooth; and narrow- to medium-bandwidth communications systems. The RSA-3408B covers dc to 8 GHz and provides 36-MHz capture bandwidth and 73-dB SFDR for applications that demand higher bandwidth and dynamic range, such as debugging of 3G mobile components and systems, design of WLANs (wireless local-area networks) and WiMax systems, demanding spectrum management, and general-purpose digital-RF debugging.

To display live spectra, the RSA3300B series' and RSA-3408B's DPX waveform-image-processing technology uses dedicated real-time hardware to process more than 48,000 input-signal-spectrum measurements/sec-orders of magnitude more information than spectrum analyzers without a DPX display. This processing speed minimizes the analysis gaps inherent in swept-spectrum and vectorsignal analyzers.

Besides live RF, the waveform-image processor provides an intensity-graded persistence display that holds anomalies until the eye can see them and shows the history of occurrences of dynamic signals, providing immediate feedback on signal variations over time. This display enables engineers to rapidly see transients and signals that are either completely invisible or that a user can deduce only after time-consuming offline analysis.

According to Tektronix, the 15-MHz-bandwidth RSA-3000B and the 36-MHz-bandwidth RSA3408B are the only midrange spectrum analyzers that offer frequency-domain triggering. This function uses the FMT (frequency-mask-trigger) feature to find interfering and transient signals that no other instrument can, eliminating potential system instabilities from a design before they can cause problems. By displaying a seamless record of frequency and power changes over time, the new analyzers can solve transient problems, including modulation switching on software-defined-radio systems, identification of rogue pulses in radar transmission, and dynamic-modulation changes during a WLAN transmission.

The US suggested prices for the RSA3303B begin at \$32,900; RSA3300B and RSA3408B software options handle 3G, WiMax, WLAN, RFID, signal-source, and general-purpose modulation and RF analysis.

-by Dan Strassberg **Tektronix Inc,** www.tek. com/products/spectrum\_ analyzers/rsa3000.

# Babies, bouquets, and big events courtesy of Analog Devices ICs.

#### **Our newest camera innovations**

#### AD9920A: Highly Integrated Analog Front End (AFE)

Low noise image capture helps to deliver higher quality images at higher ISO settings. This high performance AFE consumes 50% less power than competitive AFEs.

#### SSM2301: Fully Integrated, High Efficiency Class-D Audio Amplifier

Our low power Class-D audio amplifier combines the ability to efficiently deliver more power out, with excellent THD and SNR audio fidelity, for a better remote playback experience.

**ADV7520NK: 80 MHz, HDMI Transmitter** This HDMI transmitter enables faithful display of your high resolution photos on

display of your high resolution photos on HDTV and consumes a fraction of the standby current of competitive solutions.

#### Digital still cameras are all about the user experience that's why more than half have ADI inside

Crisp images. Clear remote audio. Long battery life. When the leading manufacturers of digital still cameras (DSCs) seek to deliver the best user experience, they turn to Analog Devices for its proven credentials as an active partner on the design team. Our years of experience and applications expertise help manufacturers bring the newest DSCs to market on time and on budget. But it's not only camera designers and users who benefit from our extensive portfolio of high performance analog and mixed signal ICs—we're also at the forefront of medical, automotive, communications, and industrial technologies. Wherever user experience defines the design, Analog Devices defines the possibilities.

To experience what Analog Devices ICs can do for your designs, call 1-800-AnalogD or visit *www.analog.com/digitalcameras.*

#### VOICES Harley Feldberg: the pulse of the industry

Sometimes, the best way to get the pulse of the industry is to talk with electronics distributors who are out there on the street every day. Recently, *EDN* spoke with Harley Feldberg, president of Avnet EM (Electronics Marketing), about the economic situation, the growing role of Avnet in the design community, and the changing role of Asia in the industry. Portions of that interview follow. For more, go to ww.edn.com/ article/CA6530480 and www.edn.com/080306p1.

#### Are you concerned about the economic slowdown?

That's obviously the big question. I think the market, in lieu of good news, has been assuming bad news. The technology industry has been adopting a half-empty posture. After [our December analyst] conference call, we have one-on-one [calls] with the top analysts that follow our stock. That's where you get into the more meaningful questions and, in those one-on-ones, they generally asked, 'Are we concerned?' Of course we are concerned. All we can do because we are not economists, though, is relay what we are actually seeing. Now through the December quarter, we're just not seeing indicators [of a significant slowdown]. We're not seeing evidence of cancellations. We're not seeing unusual pricing pressure. It's really just a normal, rational market.

#### So, you have no concerns about inventory or leadtimes with the economic situation?

A No. I think the only concern that I have is if we go into a severe global recession. Again, I'm not an economist, but we don't see that on the horizon. We really see pretty steady leadtimes, pricing, and demand. Are we concerned about the United States going into a gigantic recession that would impact citizens' purchasing of electronic things, which would impact our business in Asia? Of course we are. But at least through December, we don't see any indicators of that.

#### Are there any technology areas of special interest in the coming quarters for Avnet?

We've been filling out our A line card in two areas. One [is] where there are major suppliers that don't have a major presence in distribution but are important to our customers. We've been working with those guys. Our announcement about Maxim is a good example. [The company has] always been a valuable supplier to our customers but heretofore has not been a big participant in the channel. It's not a new product line to us, but it's a new way of doing business. It's an expansion with a large suppler that previously wasn't a player.

How important is Japan for Avnet's future growth?

I always struggle to find a precise answer [to that question] because it is easy to be wrong. Numerically, as a market, it's a similar size to [that in the United States] and Europe, which makes it very attractive. Culturally, it's a market that does things differently from the West. So. if I've learned anything in the couple of years we've been focusing on Japan, it's patience. [Japan] is important, but it must be taken in the proper context. I wouldn't suggest we forecast 100% growth in 2008. We are growing, we're adding product lines, we are looking at potential acquisitions and partners, but I always temper those comments [by reminding people] that it's one [market] that requires time and patience. Ultimately, it will be a big market for us. The question is how long it will take.

You and Chief Executive Officer Roy Vallee have often spoken about balancing Avnet's growth globally. Yet it seems as though a lot of your business lately has been coming from Asia. Is this situation a red flag for you?

Not really, but it is a reality that we have to accept and deal with. Currently, our business, if you average the last two quarters, is about 30% from Asia. If you contrast that to five or 10 years ago, it's grown dramatically. What we have said in the past is that we don't believe our business will mimic our suppliers' ratio. Most of our suppliers get more than 50% of their revenue from Asia. We think that, over the next two years or so, our business will be more like a third-35% or so. What that [situation] means is learning to deal in an environment of lower gross margins but higher asset velocity. Our ability to [increase] our operating-income ratio is going to be lower. It's going to continue to improve, but the rate at which it improves is going to be lower because we are starting from a lower gross margin in Asia. With that said, our preoccupation over the last five years or so on return on capital has really allowed us to get back to the right point. Our return-oncapital matches year on year have seen progress that's really phenomenal. It's really been a by-product of learning to do business in Asia-Asia-style. It means turning assets quicker, controlling costs more readily. It does mean a different model for us, but, so far, we've addressed it successfully.

#### Do you have any closing thoughts on the year ahead?

It's a big question right now. Maybe we have guarterly amnesia. Maybe we have this conversation every guarter. But it does seem that, because of all the high-level concern about the macro market, we are all kind of on standby right now. What's the market going to do? Are we going to have a meltdown? We just don't see it, but I wouldn't want to be cavalier and suggest that we aren't watching it and aren't concerned about it. We will address whatever comes our way, but, for now, we feel pretty good about 2008.

-by Suzanne Deffree

# **Rarely Asked Questions**

Strange but true stories from the call logs of Analog Devices

#### Too Hot or Too Cold May Be Just Right\*

**Q.** Are absolute maximum and minimum temperatures as absolute as voltage or current ratings?

**A.** No! While integrated circuit manufacturers cannot guarantee devices used outside their temperature ratings, ICs do not suddenly cease to work beyond these limits. But engineers who choose to use ICs at other temperatures must determine for themselves how well they will work, and how consistent their behavior will be.

There are useful general rules. At temperatures around 185 to 200°C (the exact value depends on the process), increased leakage and reduced gain make silicon IC operation unpredictable, and accelerated dopant diffusion limits lifetimes to hundreds, or at best thousands, of hours. Nevertheless, ICs are regularly used at these temperatures in applications, such as drill head instrumentation, where degraded performance and reduced lifetime are acceptable. At slightly higher temperatures, though, operational lifetimes may become too short to be useful.

At very low temperatures, reduced carrier mobility eventually causes devices to stop working, but some circuits will function, albeit out of specification, at temperatures below 50 K.

Basic physics is not the only limiting factor. Design compromises may improve performance in one temperature range at the cost of malfunction outside it — the AD590 temperature sensor, for example, works in liquid nitrogen if it is powered and then cooled, but will not start at 77 K.

More subtle effects result from performance optimization — the commercial grade of a device (0 to 70°C) may have very good accuracy within this temperature range, but dreadful accuracy outside it, while the military grade (-55 to +155°C) of the same device may maintain

slightly lower accuracy over the wider temperature range because of a different trimming algorithm, or even from a slightly different circuit design. The difference between the grades may not only be due to different testing.

Two other issues are the behavior of the package material, which may fail before the silicon, and the effects of thermal shock — the fact that an AD590 will work at 77 K if cooled slowly does not mean that it will survive the high transient thermo-mechanical stresses of suddenly being plunged into liquid nitrogen.

The only way to use a device outside its specified temperature range is to test, test, test, and test again, thus ensuring that you understand how the non-standard temperature affects the behavior of devices from several different batches. Check all your assumptions.<sup>1</sup> The IC manufacturer may or may not be helpful and will probably not give any guarantees for out-of-temperature operation.

\* "The Goldilocks Enigma" by Paul Davies ISBN 0547053584 <sup>1</sup> "Check your assumptions. In fact, check your assumptions at the door." 'Barrayar' by Lois McMaster Bujold ISBN 2290313157

To learn more about temperature ranges Go to: http://rbi.ims.ca/5704-101

Contributing Writer James Bryant has been a European Applications Manager with Analog Devices since 1982. He holds a degree in Physics and Philosophy from the University of Leeds. He is also C.Eng., Eur.Eng., MIEE, and an FBIS. In addition to his passion for engineering, James is a radio ham and holds the call sign G4CLF.

Have a question involving a perplexing or unusual analog problem? Submit your question to:

raq@reedbusiness.com For Analog Devices' Technical Support, Call 800-AnalogD

SPONSORED BY

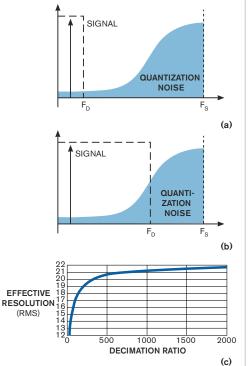

# Delta-sigma ADCs in a nutshell, part 4: noise versus data rate

his article is the last in a brief overview of the inner workings of delta-sigma ADCs. You have seen how the modulator operates in the time and the frequency domains and how it shapes the conversion-quantization noise into higher frequencies. The modulator implements an oversampling system that has an integrator and negative feedback. You've also read about the inner workings of the digital/decimator filter. This filter

reduces the high-frequency noise in the digital 1-bit stream from the modulator while passing the digitized input signal to the converter output at a reduced data rate. The combination of these two modules yields a high-resolution ADC (references 1, 2, and 3).

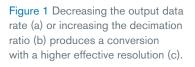

With any converter, the actual resolution is equal to the number of bits the ADC transmits. "Effective resolution" describes the useful bits from an analog-to-digital conversion as they relate to signal noise. Effective resolution is equivalent to the ADC's effective number of bits. The ratio of the modulator's  $F_s$  (sampling rate) and  $F_D$  (output-data rate) define the decimation, or oversampling, ratio, which directly impacts effective resolution. The decimation ratio, whose value ranges from four to 32,768, equals the number of modulator samples per data output.

Consider the frequency spectrum in Figure 1. Suppose that you make the output data rate a small fraction of the modulator's sampling frequency (Figure 1a). The input frequencies from zero to  $F_D$  are in the output-signal band. The effective resolution is high because the noise level is low. A higher frequency for  $F_D$  increases the convert-

er's output-data rate and decreases the effective resolution. Most of the noise from the modulator is in the higher frequencies, but you still have a lower effective resolution (Figure 1b). Figure 1c shows an example of the relationship between decimation ratio and effective resolution of a sampling ADC.

One way to increase the output-data-rate speed without changing the effective resolution is to increase the modulator-sampling rate. You can increase this rate by increasing the master clock rate to the delta-sigma ADC. With a constant decimation ratio, both the sampling rate and the power consumption increase. Also, most converters have a practical limit for the sampling rate, beyond which they do not function properly. A strong relationship exists between the decimation ratio and effective resolution. Keeping the sample rate constant and lower data rates gives you high effective resolution at the output of the converter (references 4 and 5).EDN

#### REFERENCES

Baker, Bonnie, "Delta-sigma ADCs in a nutshell," *EDN*, Dec 14, 2007, pg 22, www.edn.com/article/CA6512148.

Baker, Bonnie, "Delta-sigma ADCs in a nutshell, part 2: the modulator," *EDN*, Jan 8, 2008, pg 24, www.edn. com/article/CA6518678.

Baker, Bonnie, "Delta-sigma ADCs in a nutshell, part 3: the digital/decimator filter," Feb 21, 2008, pg 24, www.edn.com/article/CA6531581.

Antoniou, Andreas, *Digital Filters: Analysis and Design, Second Edition*, McGraw-Hill, May 15, 2000, ISBN 0070021171.

Baker, R Jacob, CMOS Mixed-Signal Circuit Design, J Wiley & Sons, June 2002, ISBN: 0471227544.

Bonnie Baker is a senior applications engineer at Texas Instruments and author of A Baker's Dozen: Real Analog Solutions for Digital Designers. You can reach her at bonnie@ti.com.

# Design with the best: Optoelectronics

CML INNOVATIVE TECHNOLOGIES WHERE INNOVATION COMES TO LIGHT

Honeywell

CREE

LIGHT BY

"Next-day delivery when I need it. *That's important.*

A website that lets me sort by price. That's important, too.

The best LED selection. *That's critical.*"

#### Design with the best brands

You'll find the best components and the best information in one site. Visit <u>www.newark.com/energy</u> to make the most of the newest advances in power management, switching efficiency, circuit protection and solid-state illumination.

Find more at www.newark.com and 1.800.4.NEWARK

A Premier Farnell Company

#### **PRY FURTHER AT EDN.COM**

+ Go to www.edn.com/pryingeyes for past Prying Eyes write-ups.

#### SanDisk V-Mate videomemory-card recorder

Since the recordings are playback-compatible. Recording time is approximately 3.6 hours in a mobile phone at a bit rate of 544 kbps and 1.8 hours on a notebook computer at 1.056 kbps. The V-Mate measures  $5.1 \times 2.6 \times 0.8$  in and costs \$80 to \$120.

000000000